- 您现在的位置:买卖IC网 > Sheet目录323 > DSP56311EVM (Freescale Semiconductor)KIT EVALUATION FOR DSP56311

�� �

�

Core� Configuration�

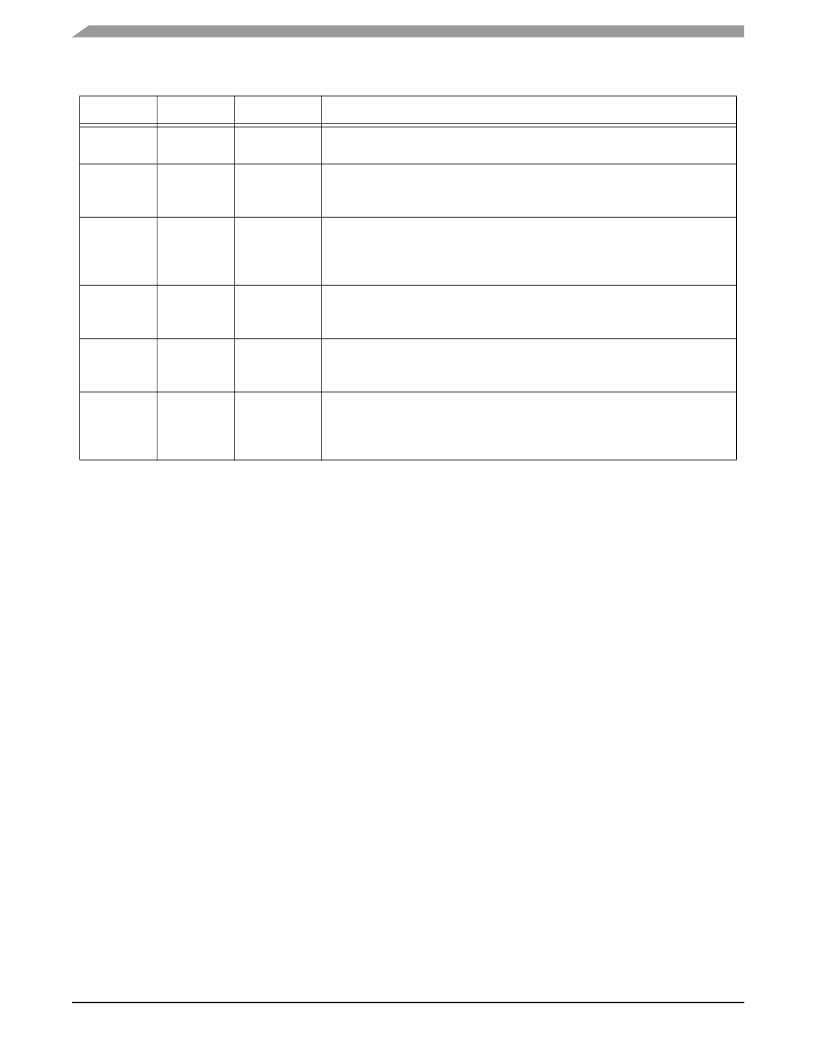

�Table� 4-7.� PLL� Control� Register� (PCTL)� Bit� Definitions� (Continued)�

�Bit� Number�

�18�

�17�

�Bit� Name�

�PEN�

�PSTP�

�Reset� Value�

�Set� to� PINIT�

�input� value�

�0�

�PLL� Enable�

�Enables� PLL� operation.�

�PLL� Stop� State�

�Description�

�Controls� PLL� and� on-chip� crystal� oscillator� behavior� during� the� stop�

�processing� state.�

�16�

�XTLD�

�0�

�XTAL� Disable�

�Controls� the� on-chip� crystal� oscillator� XTAL� output.� The� XTLD� bit� is� cleared�

�during� DSP56311� hardware� reset,� so� the� XTAL� output� signal� is� active,�

�permitting� normal� operation� of� the� crystal� oscillator.�

�15�

�XTLR�

�0�

�Crystal� Range�

�Controls� the� on-chip� crystal� oscillator� transconductance.� The� XTLR� bit� is�

�cleared� (0)� during� hardware� reset� in� the� DSP56303.�

�14–12�

�DF[2–0]�

�0�

�Division� Factor�

�Define� the� DF� of� the� low-power� divider.� These� bits� specify� the� DF� as� a� power�

�of� two� in� the� range� from� 2� 0� to� 2� 7� .�

�11–0�

�MF[11–0]�

�0�

�PLL� Multiplication� Factor�

�Define� the� multiplication� factor� that� is� applied� to� the� PLL� input� frequency.� The�

�MF� bits� are� cleared� during� DSP56311� hardware� reset� and� thus� correspond� to�

�an� MF� of� one.�

�4.6� Bus� Interface� Unit� (BIU)� Registers�

�The� three� Bus� Interface� Unit� (BIU)� registers� configure� the� external� memory� expansion� port� (Port�

�A).� They� include� the� following:�

�Bus� Control� Register� (BCR)�

�DRAM� Control� Register� (DCR)�

�Address� Attribute� Registers� (AAR[3–0])�

�To� use� Port� A� correctly,� configure� these� registers� as� part� of� the� bootstrap� process.� The� following�

�subsections� describe� these� registers.�

�4.6.1�

�Bus� Control� Register�

�The� Bus� Control� Register� (BCR),� depicted� in� Figure� 4-6� ,� is� a� read/write� register� that� controls� the�

�external� bus� activity� and� Bus� Interface� Unit� (BIU)� operation.� All� BCR� bits� except� bit� 21,� BBS,�

��DSP56311� User’s� Manual,� Rev.� 2�

�4-20�

�Freescale� Semiconductor�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DSPAUDIOEVMMB1E

BOARD MOTHER DSP563XX

DSPIC30F2010 DEVELOPMENT KIT

KIT DEV EMBEDDED C

DSTRM-KT-0181A

DSTREAM DEBUG AND TRACE UNIT

DSUT1CSU

SURGE SUPPR NETWORK W/GROUND

DTEL2

SURGE SUPPRESSOR PHONE RJ11/RJ45

DV003001

PROGRAMMER PICSTART PLUS 16C/17C

DV164035

MPLAB ICD3 IN-CIRC DEBUGGER

DV164039

KIT DEV PIC24FJ256DA210

相关代理商/技术参数

DSP56311EVMIG_D

制造商:未知厂家 制造商全称:未知厂家 功能描述:DSP56311EVMIG DSP56311EVM Sample Code

DSP56311EVMUM

制造商:未知厂家 制造商全称:未知厂家 功能描述:DSP56311 Evaluation Module Hardware Reference Manual

DSP56311FACT

制造商:未知厂家 制造商全称:未知厂家 功能描述:DSP56311 Higher performance programmable DSP for demanding voice and data applications

DSP56311UM

制造商:未知厂家 制造商全称:未知厂家 功能描述:DSP56311 24-Bit Digital Signal Processor Users Manual

DSP56311UMAD

制造商:未知厂家 制造商全称:未知厂家 功能描述:DSP56311 Users Manual Addendum

DSP56311VF150

功能描述:数字信号处理器和控制器 - DSP, DSC 150Mhz/300MMACS 150Mhz EFCOP RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSP56311VF150B1

功能描述:数字信号处理器和控制器 - DSP, DSC 24 BIT DSP

RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT

DSP56311VF150R2

功能描述:数字信号处理器和控制器 - DSP, DSC 24 BIT DSP RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT